2021 年 6 月 16 日

2021 年 6 月 16 日世界最高耐圧の酸化ガリウム縦型トランジスタの開発に成功

– 従来の1.6倍の4.2 kV耐圧を実証 –

株式会社ノベルクリスタルテクノロジー(埼玉県狭山市、代表取締役社長 倉又朗人)は、防衛装備庁が実施する安全保障技術研究推進制度(JPJ004596)の支援を受け、高耐圧の酸化ガリウム縦型ノーマリオフ MOS トランジスタ※1の基本構造の開発に成功しました。本成果を用いて酸化ガリウムパワートランジスタの開発を加速します。

ショットキーバリアダイオード(SBD)※2やトランジスタ※3に代表される半導体パワーデバイス(以下、パワーデバイスと表記)は、家電・自動車・電車・産業用機器など、世界中のあらゆる電気機器に組み込まれ、電圧や電流の制御を行っている部品です。その制御を行う際、パワーデバイスの中で電力損失が発生します。この損失を小さくすることにより、電気機器の消費電力の削減が可能となり、CO2削減による地球温暖化対策に繋がります。

酸化ガリウムは、現在パワーデバイス用材料として開発が進められている炭化ケイ素(SiC)や窒化ガリウム(GaN)より大きな、4.5 eV※4というバンドギャップエネルギー※5を有するため、より低損失なパワーデバイスを実現できる夢の新材料です。また、酸化ガリウムは融液成長法※6による結晶の製造が可能であり、高品質で大型の単結晶基板を SiC や GaN の 100 倍高速に成長することができるため低コスト化も期待できます。これらの特徴から、酸化ガリウムパワーデバイスの早期実用化に向けて、国内外の企業および研究機関が研究開発を加速しています。

■内容

当社では、酸化ガリウム単結晶基板、エピウエハ※7の製造・販売を行うと共に、SBD、トランジスタの製品化をめざして開発を進めています。

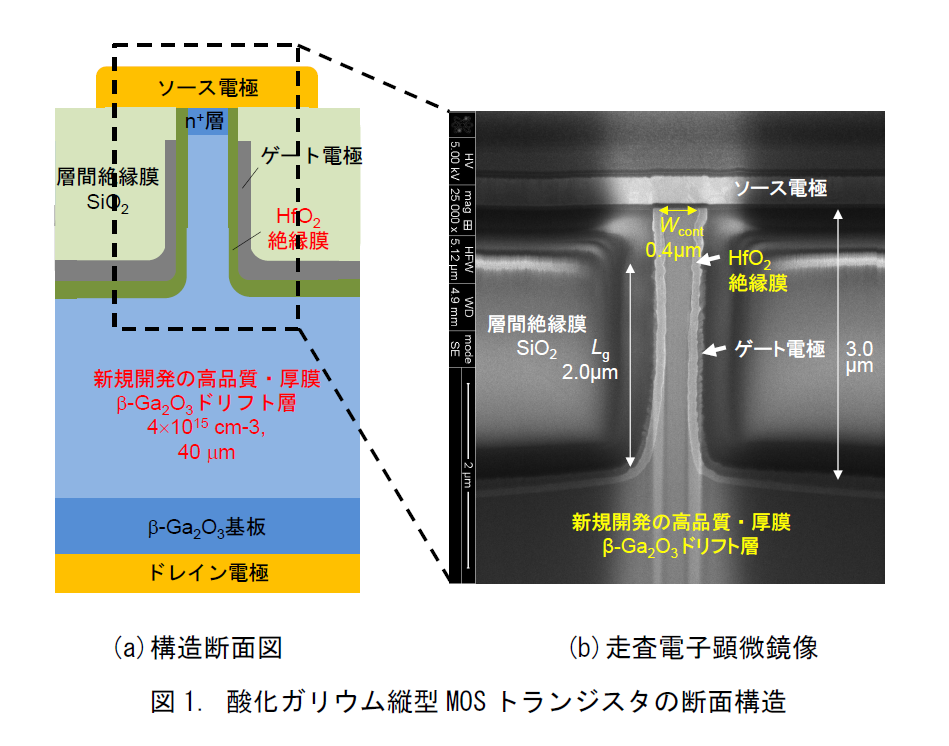

図 1 に、今回開発した酸化ガリウム縦型 MOS トランジスタの断面構造を示します。

開発したトランジスタの特徴は、

・パワーデバイスに求められる低損失化、大電流化に有利な縦型デバイス構造

・メサ幅をサブミクロン以下に狭めることで p 型導電層を用いずにノーマリオフ化ができる FinFET※8構造

・ゲート絶縁膜内の電界強度を弱めるための高誘電率酸化ハフニウム(HfO2)絶縁膜

・新規に開発した高品質・厚膜エピタキシャル成長技術を用いて形成した低ドナー濃度(4×1015 cm-3)、厚膜(40 μm)の高耐圧ドリフト層を採用している点です。

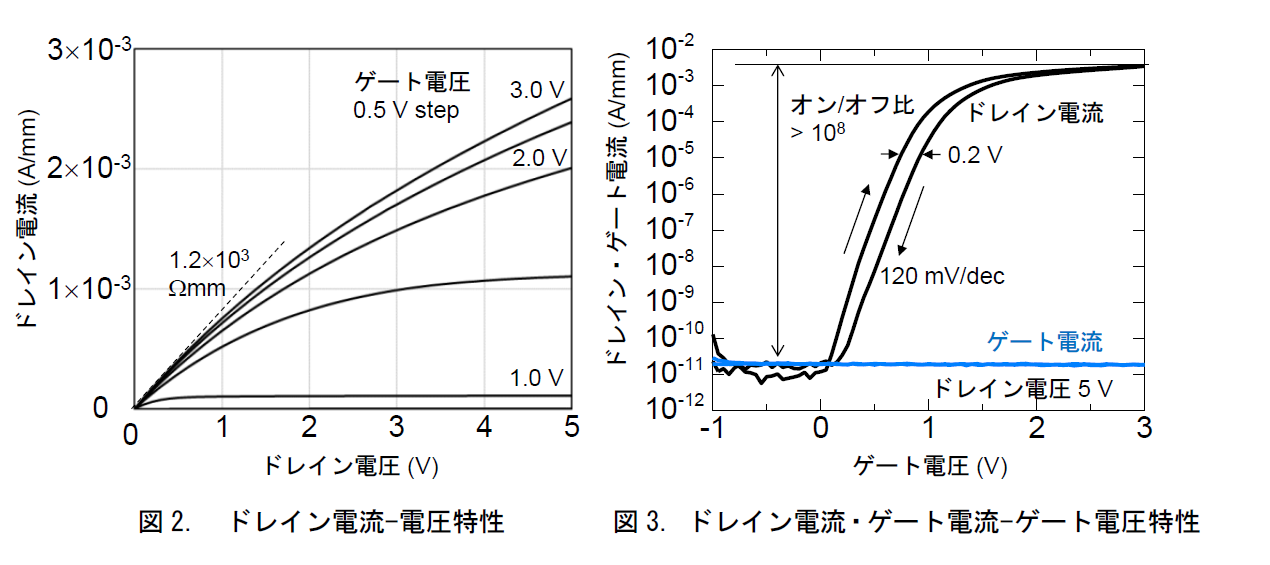

図 2 に、作製したトランジスタ(メサ幅 0.4 μm, メサ長さ 60 μm)のドレイン電流-ドレイン電圧特性を示します。ゲート電圧 0 V で電流が流れないノーマリオフ特性を示し、最大電流密度は 2.6 mA/mm、オン抵抗は 1.2×103 Ωmm を示しました。今回試作したトランジスタでは、ソースの n+層とチャネル層は 0.4 μm 程度離れておりソース抵抗が高いと推測しています。デバイス設計を改良することにより、さらにオン抵抗の低減が可能と考えています。

図 3 に、ドレイン電圧 5 V 印加時のドレイン電流およびゲート電流のゲート電圧依存性を示します。ドレイン電流オン/オフ比は 8 桁以上と大きく、サブスレッショルド係数※9は 120 mV/decade、ゲートリーク電流は測定限界以下であり、良好なトランジスタ特性が得られました。一方、ドレイン電流-ゲート電圧特性に 0.2 V 程度のヒステリシスがみられており、今後 MOS ゲート界面の改善が必要であることもわかりました。

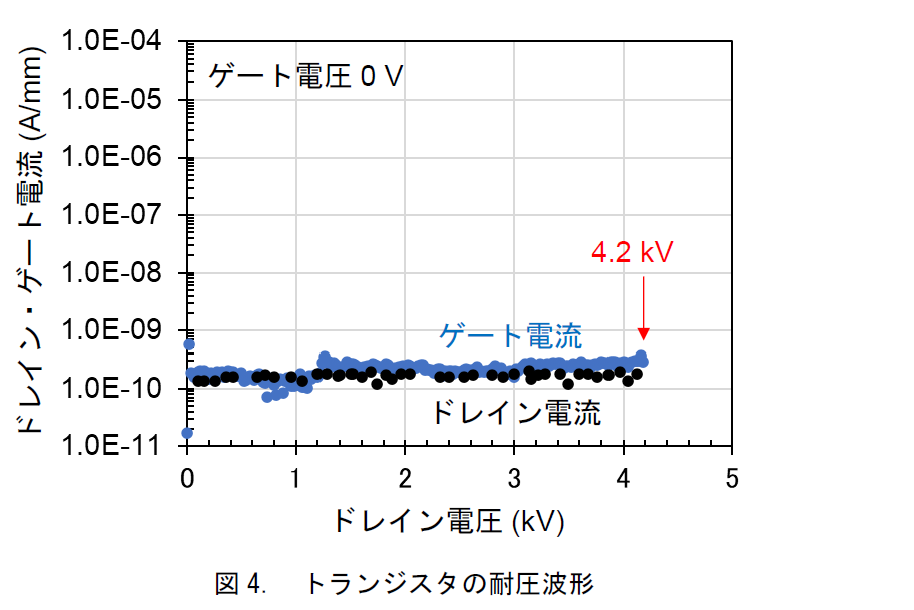

図 4 に、ゲート電圧およびソース電圧を 0 V に固定してドレイン電極に正の電圧を印加した時のドレイン電流、ゲート電流特性を示します。FinFET 構造によるゲートの制御性向上効果と、メサ加工底面の高誘電率の HfO2 絶縁膜の効果で、ドレイン電圧を 4 kV 程度まで印加してもドレインリーク電流、ゲートリーク電流の発生は有りませんでした。また低ドナー濃度(4×1015cm-3)、厚膜 40 μm の高品質エピタキシャル層をドリフト層に採用することより、これまでの報告値 2.6 kV(W. Li et al., IEDM19-270)を大きく上回る耐圧 4.2 kV(従来の 1.6 倍)が得られました。この時のメサ加工底面の酸化ガリウムドリフト層中の最大電界強度を見積もると 2.5 MV/cm になります。2 次元デバイスシミュレーションによれば、ゲート電極端にこの数倍の強度の電界集中が発生していることから、今後、電界集中を緩和する電極終端構造を導入することにより、更なる高耐圧化、低オン抵抗化が可能と考えています。

■今後の展開

今回のデバイス試作で明らかになった課題の解決を進めると共に、素子の大型化、大電流化を図ります。2025 年度に 600-1200 V の中耐圧デバイスから量産を開始し、3000 V 以上の高耐圧デバイスの量産準備を進めます。中耐圧領域では、酸化ガリウム半導体の特徴である低コストを強みに電気自動車等への応用を、高耐圧領域では低損失を強みに風力発電、直流送電、スマートグリッド、パルス電源等への応用を目標に開発を進めます。

■用語解説

※1 MOSトランジスタ

ゲート金属(Metal)/絶縁膜(Oxide)/半導体(Semiconductor)構造を用いてドレイン電流を制御するトランジスタ

※2 ショットキーバリアダイオード (Schottky barrier diode: SBD)

ショットキー電極と半導体との接合によって生じる電位障壁を利用したダイオード。低い順方向電圧と、低スイッチング損失を特長とする。

※3 トランジスタ

増幅、またはスイッチ動作をさせる半導体素子。MOSトランジスタやサイリスタ、IGBTなど、構造や動作原理の異なる様々な製品がある。

※4 eV(エレクトロンボルト)

自由空間内で一つの電子が1 Vの電圧で加速されるときのエネルギーを1 eVと表記する。

※5 バンドギャップエネルギー

固体内電子の、伝導帯の最も低いエネルギーレベルと価電子帯の最も高いエネルギーレベルの間で、電子が存在できないエネルギー状態。金属ではバンドギャップはゼロであり、絶縁体では大きな値となる。半導体はこの中間にあり、バンドギャップの大きさによりその伝導特性が大きく変化する。

※6 融液成長法

結晶化させたい材料をるつぼの中で融点以上に加熱して融解させた後、種結晶を接触させてゆっくり温度を下げることで単結晶を得る方法。チョクラルスキ法やフローティングゾーン法、Edge-defined film-fed growth法などが有名。

※7 エピウエハ

単結晶基板上に結晶膜が形成されたウエハ。主に結晶膜に機能を持たせるため、結晶膜の品質が重要となる。

※8 FinFET構造

ゲートがチャネルの2面あるいはチャネルを包むように位置しダブルゲート構造を形成しているトランジスタ。fin(魚のひれ)の形状をしていることからFinFETと呼ばれる。

※9 サブスレッショルド係数

トランジスタのオフ性能を示す性能指標で、電流量が一桁増えるのに必要なゲート電圧。室温での理想値は60 mV/decでMOS界面の品質等で増加(劣化)する。

【問い合わせ先】

株式会社ノベルクリスタルテクノロジー

《研究内容》営業部 TEL:03-6222-9336

《報道関係》上記に同じ

株式会社ノベルクリスタルテクノロジーは、株式会社タムラ製作所のカーブアウトベンチャーおよび国立研究開発法人情報通信研究機構の技術移転ベンチャーとして設立されました。